SMASH 7.6

SMASH 7.6.0 mixed-signal simulator

significantly speeds up OP/DC and transient

analyses of analog and mixed designs in

advanced nodes by a gain between x2 and x6.

These major speed-up gains have been

possible thanks to new methods and algorithms

without losing simulation accuracy, as merge of

identical SPICE instances, improve evaluation

of MOS transistors, RC reduction methods and

new Solver.

All these features allow SMASH to be as fast or

even to overtake the major fastest golden spice

simulators, while ensuring accuracy of a single

solver SPICE simulator.

SMASH is now supporting SystemVerilog language for RTL synthesizable simulations, thanks to the integration of Verilator. Verilator is open source Verilog/SystemVerilog simulator. Verilator converts Verilog HDL modules to C++ models which are simulated by SMASH.

SMASH 7.5

SMASH 7.5.0 mixed-signal simulator speeds up transient analysis of leading-edge analog and mixed designs by up to 1.5X compared to previous release.

Moreover, with SMASH 7.5.0, convergence of OP and DC analyses has been strongly improved and speed up by 10X or more, especially for mixed-signal circuits.

Now SMASH 7.5.0 supports TSMC Model Interface (TMI) aging flow to simulate Hot Carrier injection (HCI) and Bias Temperature Instability (BTI) effects in design for reliability validations.

SMASH 7.4

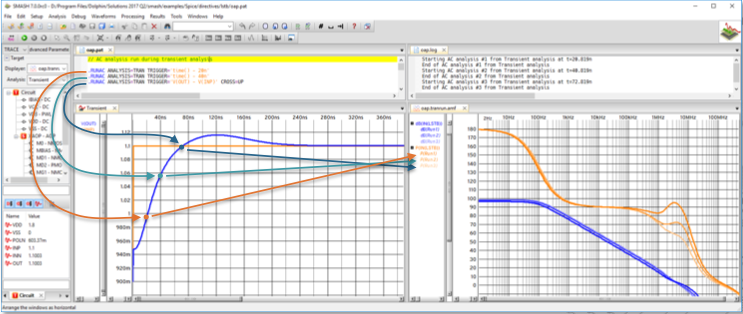

With SMASH 7.4, for circuits with thousands of MOS devices in advanced process nodes and/or post-extractionRC, designer productivity has been enhanced by improving and accelerating transient analysis by a factor x2 and more without losing simulations accuracy. Moreover, for checking the stability of closed loop systems, SMASH 7.4 provides a new method “Zeq” to enable draw of any voltage node.

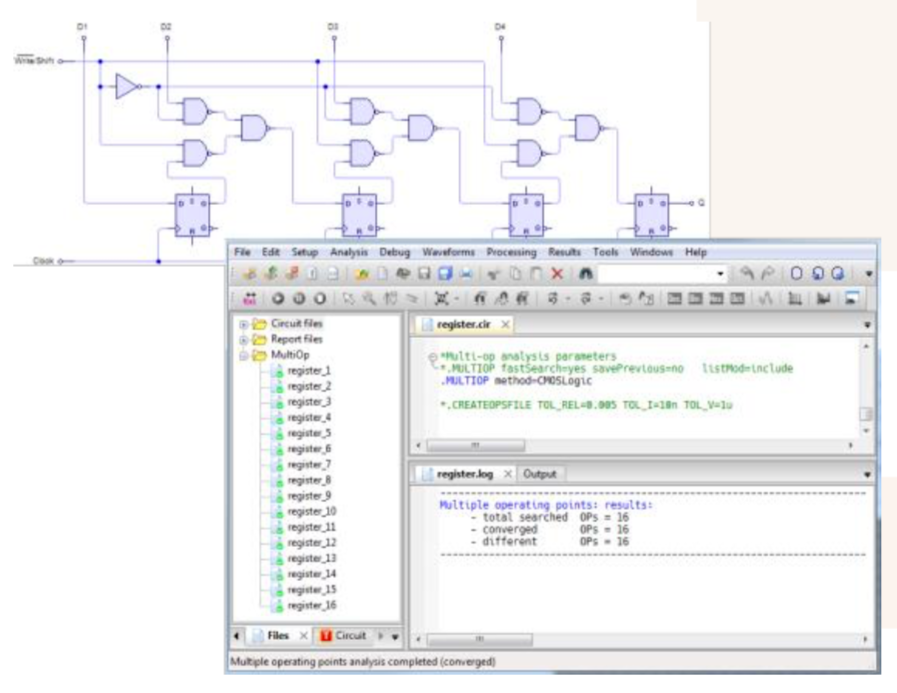

SMASH 7.3 - Find exhaustive list of operating-points

With this new CMOSLogic method used for multiple operating-points analysis, SMASH 7.3 provides designers with a solution for obtaining an exhaustive list of all possible combinations of stable operating-points of a CMOS logic circuit. This feature simplifies and speeds up the characterization of multi-bit standard cells.

SMASH 7.2 - New custom static electrical rules checking

SMASH 7.2 provides new API functionalities to scan analog circuit across DEVICE connections and to verify your own custom Static Electrical Rules Checking.

An example part of the installation kit enables to detect automatically and quickly all MOS transistors with gates directly connected to supply sources, without launching any simulation.

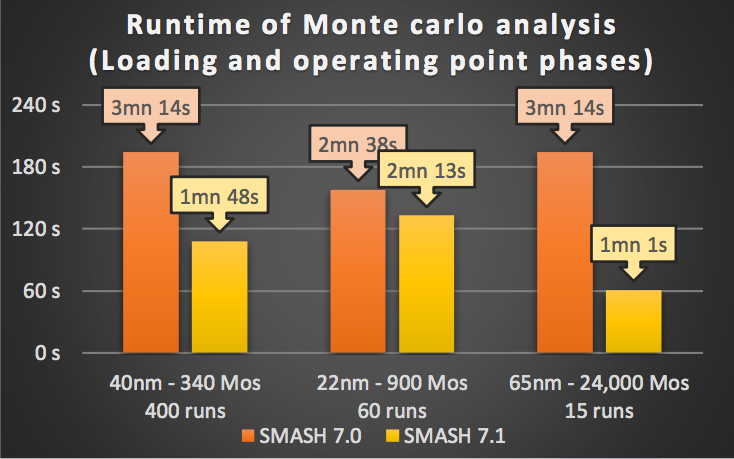

SMASH 7.1 - Optimize monte carlo analysis

Accelerating Monte Carlo Analysis is crucial because designs in advanced process-node have much larger variation and need to run thousands or even millions of statistical simulations.

Thus, with SMASH 7.1, for circuits with thousands of MOS devices, Monte Carlo analysis has been sped-up by accelerating loading phase of each run by a factor of up to x3.

SMASH 7.0 - 64-bit native application

Starting from now, all our EDA solutions will only be available in 64-bit versions for x86_64 platforms with Microsoft Windows Vista/7/8/10 or with RedHat Enterprise Linux 6 (RHEL6) and compatible Linux distributions.

Native 64-bit applications allow to overcome the limitations of 32-bit versions, such as loading large designs and simplifying installations on a 64-bit Linux OS.

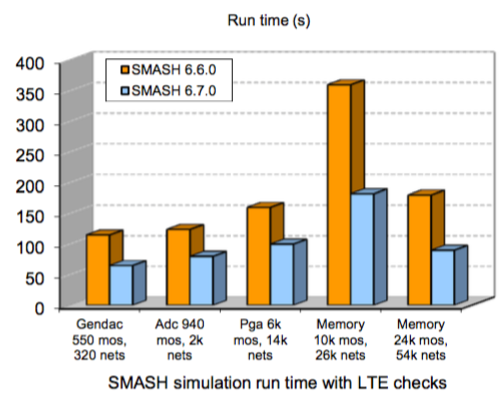

SMASH 6.7 - On the road towards slash

SMASH 6.7 significantly improves the speed and the accuracy of SPICE simulations, and makes the installation easier thanks to a new installer.

SLASH, merging SLED with SMASH, will provide an integrated user experience with a unified user interface for schematic driven simulation.

SMASH 6.6 - For increased efficiency

SMASH 6.6 delivers ergonomic enhancements to constantly improve the overall user experience and productivity.

SMASH 6.6 also provides many features for improving the interoperability of SMASH with other analog and logic simulators.

Dolphin Solutions are ideal for small to medium size companies who target using affordable state-of-the-art design solutions with no compromises on performances or innovation.

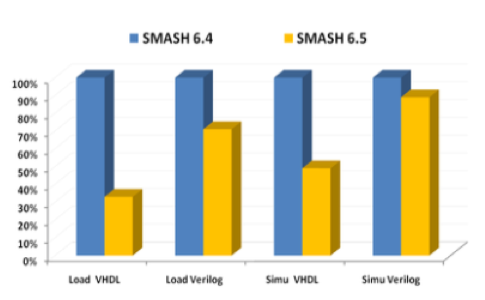

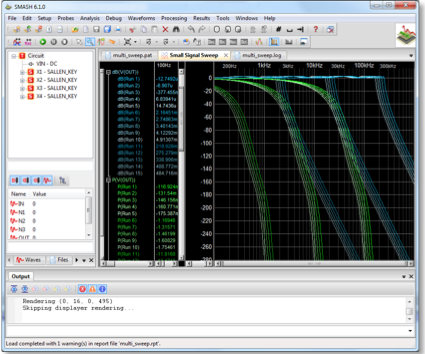

SMASH 6.5 - Hight speed SMASH simulations

Staying on the cutting edge of simulator performance, SMASH 6.5 makes three major steps forward:

Logic simulations

- Thanks to a new optimization in the logic event-driven simulator, SMASH speeds-up simulations x2 for VHDL circuits and gains 10 % for Verilog-HDL designs

- Loading of logic circuits is faster thanks to smart optimizations

Analog simulations

- Analog operating-point runtime is shorter for large circuits: from x2 to x5 faster

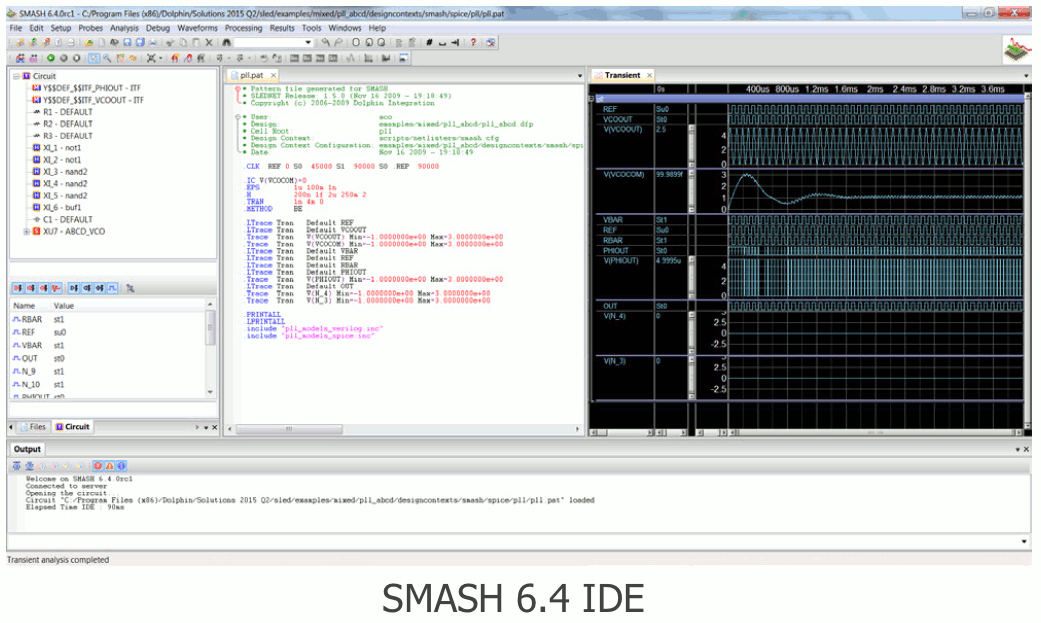

SMASH 6.4 - Speed-up to improve productivity

Staying on the cutting edge of simulator performance, SMASH 6.4 makes 3 major steps forward:

- Thanks to a new analog solver, SMASH shortens simulations of big analog circuits from weeks to days.

- Loading of logic circuits is up to 2 times faster thanks to the use of a new compiler.

- Better speed and memory performance under Linux with a SMASH native application.

SMASH 6.4 also delivers long-awaited features such as the "Magnetize" and "Transient Continue" and some user friendly IDE enhancements to constantly improve the overall user experience and productivity.

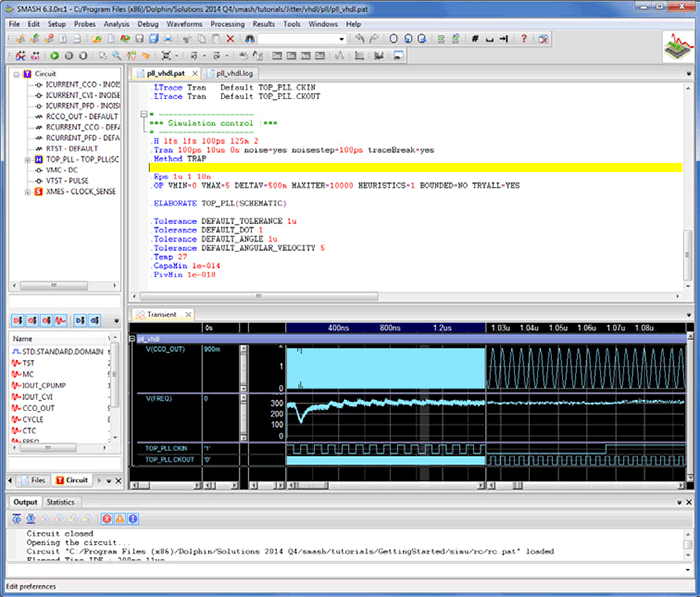

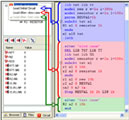

SMASH 6.3 - SMASH new generation

Most of our users are aware that Dolphin Integration has been preparing major changes in SMASH to increase our users’ productivity with:

- A new IDE sporting a new waveform viewer

- An upgraded implementation of the already bestin- class VHDL and VHDL-AMS language compliance and simulation engine

SMASH 6.3 cumulates these enhancements to significantly improve user experience.

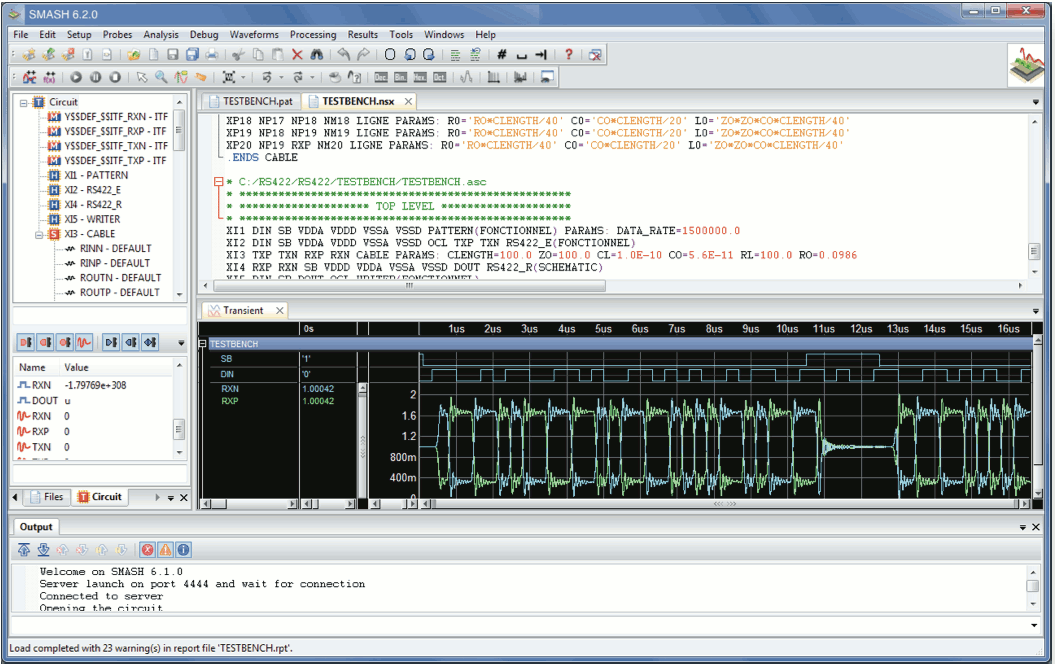

SMASH 6.2 - Back to the Future

Most of our users are aware that Dolphin Integration has been preparing major changes in SMASH to increase our users’ productivity with:

- A new IDE sporting a new waveform viewer

- A new implementation of the VHDL and VHDL-AMS standards

SMASH 6.2 is the opportunity to test these improvements in the field in your own environment and share your feedback and needs for the future.

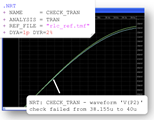

SMASH 6.1 Efficient Waveform Viewer - Modern User Interface

SMASH 6 provides a brand-new and efficient waveform viewer, for analysis of mixed-signal simulation results, as well as a new styled user interface enabling users to access and configure more easily the powerful analyses provided by the mixed-signal simulator SMASH.

SMASH 6.0 Efficient Waveform Viewer - Modern User Interface

SMASH 6.0 provides a brand-new and efficient waveform viewer, for analysis of mixed-signal simulation results, as well as a styled user interface enabling users to access and configure more easily the powerful analyses provided by the mixed-signal simulator SMASH.

SMASH 5.20 Improved Capabilities for Analog Design

SMASH 5.20 provides enhanced features and improvements to ease analog design, optimization and debug, including mixed-signal behavioral modeling. SMASH also enhances state-of-the-art logic design by enabling the verification of the impact of noise on logic signals using dedicated noise sources, previously only available for analog designers.

SMASH 5.19 Extended modeling and mixed-signal capabilities

Behind every good simulator there is a good designer! The goal of Dolphin Integration's EDA Solutions and particularly SMASH is thus to improve modeling capabilities and

designers' productivity.

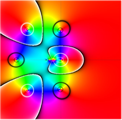

SMASH 5.19 provides enhanced features for mixed-signal design including characterization of logic designs with Monte Carlo and Sweep analyses plus an innovative

domain coloring viewer to locate and navigate through poles and zeros both in the phase and the magnitude domain.

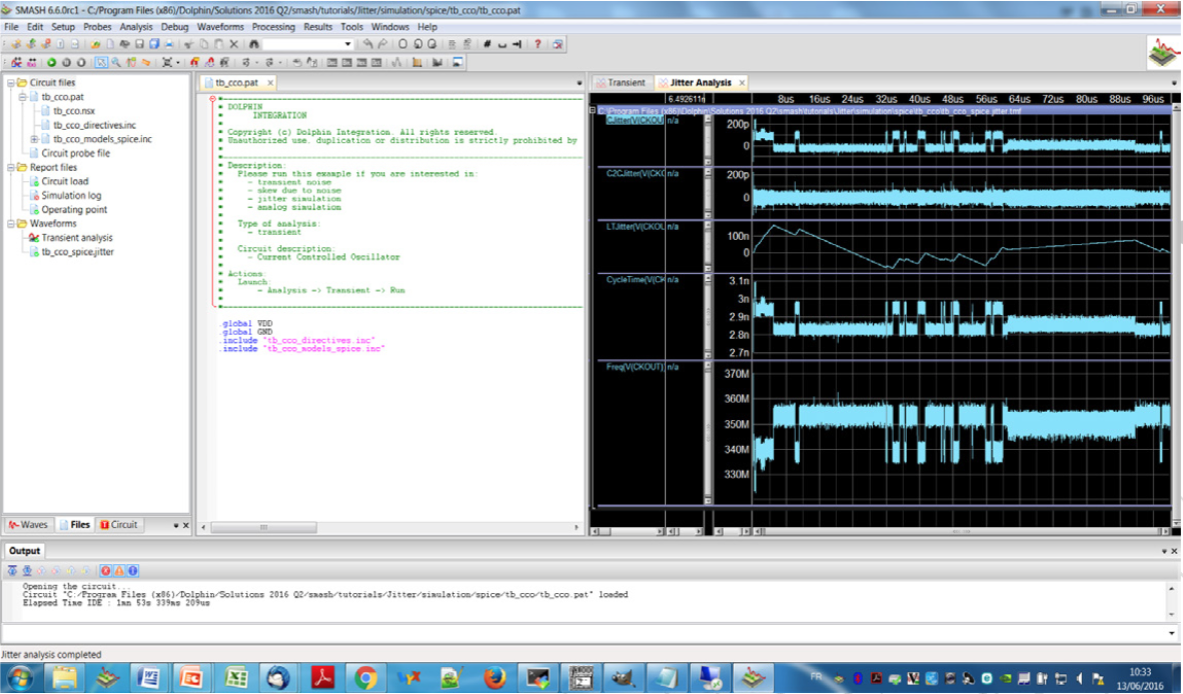

SMASH 5.18 Mixed-Signal Behavioral Modeling

The rising complexity of circuits, along with the spread of mixed-signal designs, have led to the generalization of powerful mixed-signal behavioral modeling languages

such as Verilog-AMS. However, good compliance with language standards is not sufficient to assist designers in the challenging task of modeling. The required support of

additional language syntaxes for behavioral descriptions must come with features focused on easing analog and mixed-signal modeling.

SMASH 5.18 provides innovative features for model creation, such as the identification of poles and zeros for transfer functions, but also for mixed-signal design

characterization using FFT and Jitter analysis on logic signals.

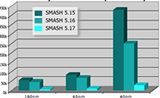

SMASH 5.17 Selective modeling and simulation

Selective modeling and simulation at different abstraction levels requires that simulation performance and accuracy trade-offs be taken into account. It is not possible

to give a general recommendation on which level of abstraction should be used, or which performances or effects should be modeled. All abstraction levels have useful

applications depending on the specific performance(s) to be verified.

SMASH 5.17 focuses on delivering new features to improve modeling capabilities while still increasing the computation speed.

SMASH 5.16 Compliance, Speed & Ease of Use

State-of-the-art analog and mixed-signal design requires analysis capabilities allowing to automate and secure multiple design steps while simplifying the investigation

and debug of mixed-language designs. While the circuit browser gives direct access to instances and models in the netlist, error and warning messages issued by SMASH

now contain clickable file and line number information for efficient debugging.

SMASH 5.16 delivers new analyses dedicated to analog design, along with Verilog/Verilog-A behavioral improvements both for logic testbenches and for analog

modeling.

SMASH 5.15 Interoperability, Compliance & Speed

As the complexity of circuits increases, the time required to perform verifications explodes, especially when using a traditional full SPICE, so-called full-chip,

approach. The only viable solution is to use a multi-level approach where parts are modeled at higher abstraction levels, with equivalence checking to ensure

appropriate accuracy of behavioral models, in order to speed-up complete circuit or system simulations.

SMASH 5.15 delivers major speed and capacity improvements along with mandatory analog equivalence checking: a must for analog behavioral modeling!

SMASH 5.14 Interoperability, Compliance & speed

The Application Hardware Modeling (AHM) approach consists in checking an overall function performed jointly by parts of the system, comprising some Virtual Component

(so called ViC or silicon IP blocks) within a SoC assembled on the PCB with discrete components, such as Quartz, PMIC, or MEMS, along with application software.

Assembling such Application Schematics (ASC) requires compliance with a variety of models at different description levels in order to perform complete multi-level, up

to multi-domain, and mixed-signal design performance verifications.

SMASH 5.14 delivers major enhancements for designer productivity!

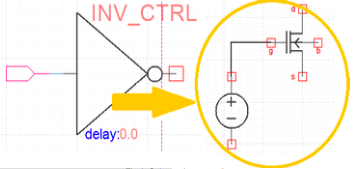

SMASH 5.13 Interface Devices, Mixed SPICE & Verilog-A, Hierarchical Tolerances

The design and verification of systems, integrating ever more features, increases the complexity of Virtual Tests needed to check that specifications are met.

Multi-level verifications have become mandatory to ensure right-on-first pass designs of multi-domain systems. Each part of the system must be modeled at the

appropriate level, with the adequate hardware description language, depending on the required accuracy for measurement of characteristics.

SMASH 5.13 increases the flexibility for mixing hardware description languages and provides straightforward configuration of hierarchical tolerances.

SMASH 5.12 Increased Speed & Capacity

SMASH 5.12 enhances its leadership position with functionalities for Logic and Mixed Signal (LMS) as it now satisfies two crucial requirements for the SoC Integrator:

It provides new circuit monitoring capabilities, akin to real-time "Detectors", leveraging on-line and conditional expressions, supervised by an "Expression Watch

Panel"!

It simultaneously provides a significant improvement for the capability of Virtual Testing thanks to Homotopy based heuristics for detection of multiple

operating-points.

SMASH 5.11 Efficient Mixing of Blocks

Performing true mixed-signal simulations, as needed by a growing proportion of SoCs, requires bringing together analog blocks, from a schematic based analog design flow

on a purely analog simulator, and logic blocks, from a batch based HDL design flow on a purely logic simulator. As the mixed-signal simulator for SoCs, SMASH provides

both the analog and logic capabilities to directly simulate with the original models, while adding the circuit and testbench setup capabilities needed to perform

complete mixed-signal simulations.

SMASH 5.11 delivers enhanced ease of simulation setup and analysis while simplifying reuse of analog blocks with HDL in mixed-signal simulations!

SMASH 5.10 Analog Power Analysis & Debug

To overcome SoC integration challenges for increased performance, higher density, and reduced power consumption, designers must employ hierarchical budget allocation

and analysis techniques. Constraints must be assigned harmoniously to the components of the System for power, noise...

In order to maintain its lead in diagnostic know-how, not only does SMASH provide hierarchical extraction and tracing of power and noise, but it facilitates Virtual

Test by enabling floating net detection during simulation to spot high impedance nets otherwise noticed too late during real test.

SMASH 5.9 Mixed signal Debug

SoC developers spend 70% of their time debugging their design and analyzing unexpected or out-of-specification results. Improving productivity is therefore essential for the time-to-market requirements of today’s SoC. To that end, SMASH 5.9 introduces debug techniques, which have been successfully used in application software development, and adapts them to the world of transient simulation on HDL-AMS descriptions for efficient back-tracing on break points, in association with graphical access to the hierarchy of the design. Analog designers will appraise further improvements in their domain, such as new and updated SPICE models, phase noise extraction...

SMASH 5.8 Mixed signal Diagnosis

SMASH 5.8 extends its capabilities for mixed signal code-coverage and sensitivity-analysis up to detecting flaws in Virtual Testbenches and to identifying circuit weaknesses for the DfM conscious designer. Improvement on the block-busting GUI features facilitate further the adjustments of speed versus accuracy, as well as tracing, now augmented for a hierarchical view applicable to mixed signal design.

SMASH 5.7 Empowered Mixity

SMASH 5.7 is loaded with innovative features which contribute to increasing the productivity of logic, analog and mixed signal designers. With good estimates of power consumption in logic circuits, designers can make an educated selection of low-power architectures and of logic blocks.

Now, for the first time, a simulator popularizes the setup of parameters to obtain the appropriate speed/accuracy tradeoff for a given Virtual Test.

SMASH 5.6 Verilog-AMS joining VHDL and SPICE

As the market is moving to nanometer technologies, the critical issue of transient noise takes a new urgency due to the sensitivity of analog and mixed-signal circuits, and even pure logic circuits. This is of course the case for PLL or oscillator designs, but also for evaluating the impact of noise injected by logic onto analog circuits.

SMASH 5.6 eases the practice of transient noise analysis, while leveraging model specific noise equations such as TSMC specific equations.

SMASH 5.5 enriched with Verilog-A

Verilog-AMS benefits designers by allowing them to describe and simulate analog and mixed signal designs using a top-down design methodology as well as the traditional bottom up approach. Moreover, Verilog-AMS provides powerful structural and behavioral modeling capabilities for systems in which the effects of, and interactions among, different disciplines like electrical, mechanical and thermal are important.

SMASH 5.5 extends its natively mixed-language and mixed-signal single kernel to Verilog-A with seamless hierarchical mixing with SPICE.

SMASH 5.4 for Design Reliability & Yield

Confronted with ever larger circuits and ever smaller fabrication technologies, Design Reliability & Yield investigation, beyond mere assessment, is required in order to obtain acceptable fabrication yield. Obviously, for effective RoI, the ever increasing fabrication cost mandates single-spin tape-outs!

SMASH focuses on enhancing Design Reliability Analysis as well as simplifying and empowering Virtual Characterization.

SMASH 5.3

Due to the ever-lasting need for performance improvements, mixed signal designers face the on-going pressure of time-to-market and of cost reduction. The main improvements provided in SMASH 5.3. are focused on increasing designers’ productivity for optimizing the reliability and yieldof complex circuits.

SMASH 5.2

Beyond the stage when new functionality was on high demand, the last couple of years has led SMASH to focus rather on Designer's productivity gains. Concern for return on assets has generated new demands, ranging from Virtual test and Diagnostics, via the specialization for Front-End and Back-End, to yield assessment.

- Thanks to a new patent (pending), a proprietary "FAST" mode speeding up analog simulation, for high-risk circuits where small time steps are needed with intensive

iterations, 3 times with an accuracy loss of 1%, and up to 7 times faster when accuracy can be relaxed!

No other contender can do this... - SMASH interfaces directly with Simulink/MATLAB. Users can leverage our unique mixed-signal multi language simulation technology in a system simulation: the ultimate top-down and bottom-up calibration and verification process that brings your HDL blocks back into your system specification!

SMASH 5.1

Upon mixity improvements SMASH 5.1 introduces drastic speed improvements to increase designers' productivity:

- Memory optimizations for large SPICE circuits

- Impressive speed improvements for second and third order VHDL-AMS models, particularly important for complex MEMS designs

- Mixity improvements such as ordered port mapping of VHDL instances in Verilog modules

- Support of cosimulation with SystemC models (a specific tutorial is available)

- Graphic interface improvements (Windows XP look, configurable tool bar, ...)

- Highlight